# APPLICATION NOTE (DOC No. HX8218-A-AN)

## <sup>>></sup>HX8218-A

960CH TFT LCD Source Driver with Built-in T-CON

Preliminary version 02 July, 2005

Himax Technologies, Inc. http://www.himax.com.tw

## <sup>≫</sup>HX8218-A

960CH TFT LCD Source Driver with Built-in T-CON

### **Preliminary Version 02**

July, 2005

## 1. General Description

HX8218-A is a 960-channel output Source Driver with built-in TCON and DAC. The interface follows digital 8-bits serial/24-bits parallel RGB, or CCIR601/656 input signals and digital control timing signals. The DAC supports transferring digital RGB data to analog RGB data for the internal Source Driver. The TCON generates the 960x240 resolution timing to Source driver and Gate Driver.

The Source Driver implements 2 lines of sample and hold circuits. While sampling video signals, the previously sampled data can be output synchronously through driver output channels. And simultaneous or sequential sampling can be chosen for matching the pixel array type.

The timing controller provides horizontal and vertical control timing to source and gate drivers. With built-in DAC and operational amplifiers, the gamma correction can be performed and digital data is converted to analog signal and sends to source driver.

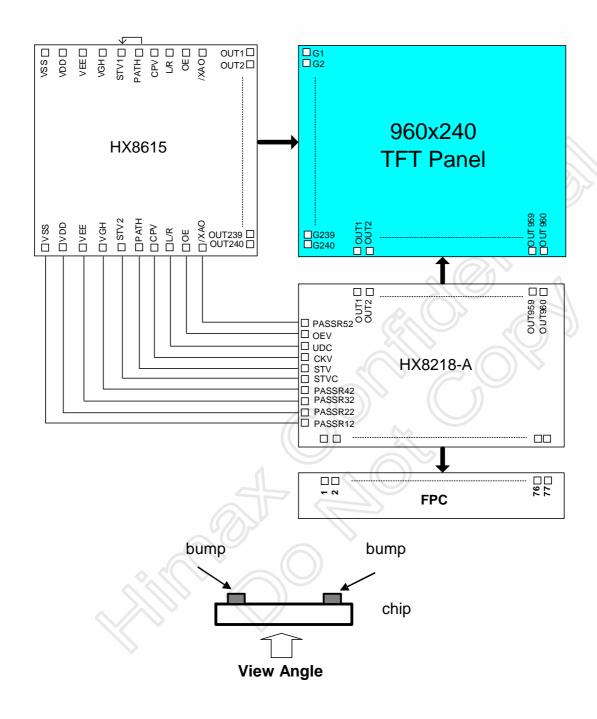

## 2. On Panel Connection (L)

Himax Confidential -P.2-

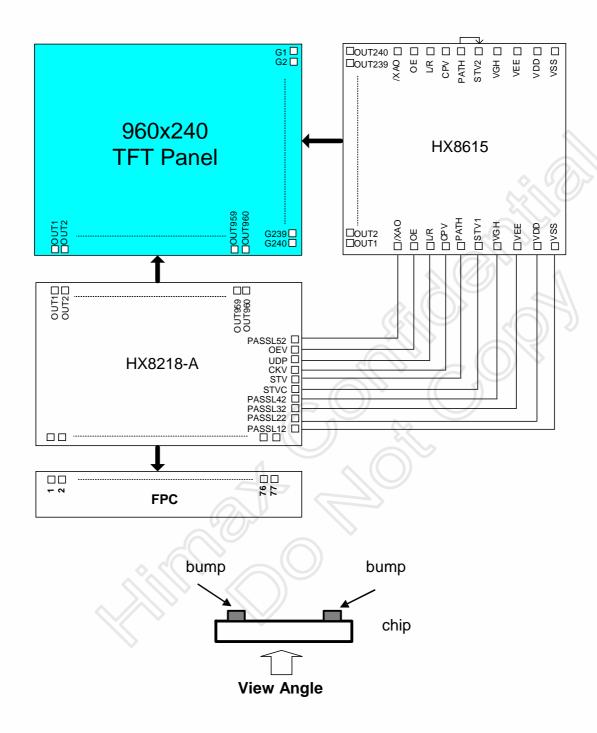

## 3. On Panel Connection (R)

Himax Confidential -P.3-

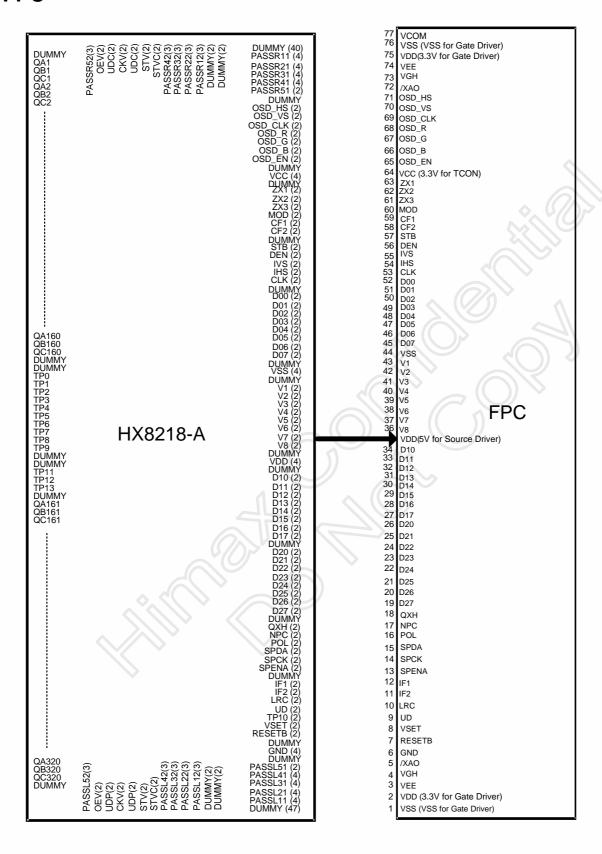

#### 4. FPC

DATA SHEET Preliminary V02

#### 5. Pin in FPC

#### 5.1 Input Data Mode in FPC

|              | D00 | D10 | D20 |

|--------------|-----|-----|-----|

|              | ~   | ~   | ~   |

|              | D07 | D17 | D27 |

| Serial RGB   | V   | Х   | Х   |

| Parallel RGB | V   | V   | V   |

| CCIR 656     | V   | X   | Χ   |

| CCIR 601     | V   | X   | X   |

#### 5.2 Input Data Format Setting

| IF2 | IF1 | Input data format    |

|-----|-----|----------------------|

| L   | L   | Serial RGB (default) |

| L   | Н   | Parallel RGB         |

| Н   | L   | CCIR601              |

| Н   | Н   | CCIR656              |

#### 5.3 Description in FPC

#### 5.3.1

OSD: If you don't want to use OSD, you just set the OSD\_EN to low and others(OSD\_HS, OSD\_VS, OSD\_CLK, OSD\_R, OSD\_G, OSD\_B) are floating.

#### 5.3.2

SPI: If you don't want to use SPI, you just set the SPENA to high and others(SPDA, SPCK) are floating.

#### 5.3.3

Gamma Voltage: Set VSET to low to use the default voltage and others(V1 ~ V8) are floating and be careful to drive the V1 ~ V8, it will influence the Gamma Voltage whatever VSET set to low.

#### 5.3.4

Color Filter: When MOD="L", delta type and others(CF1, CF2) are floating, When MOD="H", stripe type.

#### 5.3.5

Input data sequence and color filter type

CF1 defines the input data sequence in serial digital RGB mode as following tables.

#### 1. CF1="L"

| Scan direction  | can direction UD |      | Low      | High | High |

|-----------------|------------------|------|----------|------|------|

| Shift direction | LRC              | High | Low      | High | Low  |

| Data coguence   | Odd line         | RGB  | BGR      | BRG  | GRB  |

| Data sequence   | Even line        | BRG  | GB BGR E | RGB  | BGR  |

#### 2. CF1="H"

| Scan direction  | UD        | Low  | Low | High | High |

|-----------------|-----------|------|-----|------|------|

| Shift direction | LRC       | High | Low | High | Low  |

| Data assurance  | Odd line  | RGB  | BGR | GBR  | RBG  |

| Data sequence   | Even line | GBR  | RBG | RGB  | BGR  |

For the color filter type, set MOD="H" for stripe type and the CF1&CF2 definition will have no meaning. Set MOD="L" for delta color filter and CF2 defines which kind of delta type color filter is used.

1. CF2="L", delta type 1

| I | R |  | R |   | G |   | В | ı | ₹ | ( | 3 |   | В |  |

|---|---|--|---|---|---|---|---|---|---|---|---|---|---|--|

|   | В |  | R |   | ( | G | В |   | R |   | G |   |   |  |

| ı | ₹ |  | G |   | В | 1 | R |   | G |   | В |   |   |  |

|   | В |  | F | ? | 4 | G |   | В | R | 2 |   | 3 |   |  |

2. CF2="H", delta type 2:

|   | R | G |   | G B R |   |   | G |   | В |   |   |  |

|---|---|---|---|-------|---|---|---|---|---|---|---|--|

| ( | G |   | В | F     | ₹ |   | G |   | В |   | R |  |

|   | R |   | G |       | Е | 3 | R |   | G | j | В |  |

| ( | G |   | В | F     | ₹ |   | G | E | 3 |   | R |  |

5.3.6

Zoom Mode: The zoom in/out function is only supported in CCIR601/656 input mode in Strip type.

5.3.7

Hardware Global Reset: Low active. Normally pull high.

5.3.8

VCOM: VCOM and POL are inphase.

## 6. Power ON/OFF sequence

To prevent the device from damage due to latch-up, the power ON/OFF sequence shown below must be followed.

Power ON: VCC, GND → VDD, VSS → V1~V8 Power OFF: V1~V8 → VDD, VSS → VCC, GND

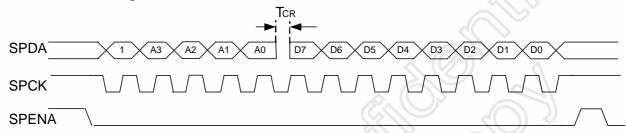

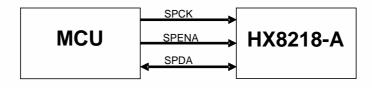

#### **7. SPI**

#### 7.1 Description

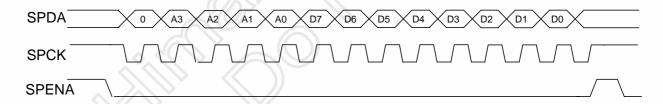

#### SPI "read" timing

- (1) Make a clock (2 MHZ) for SPCK.

- (2) Set SPENA low to let the SPI valid.

- (3) Send "1" in the MSB to show reading the SPI and the address 4-bits (A3: MSB, A0: LSB) in the rising edge of the SPCK then wait a half of the SPCK to read the data(D7: MSB, D0: LSB) in the falling edge of the SPCK.

#### SPI "write" timing

- (1) Make a clock (2 MHZ) for SPCK.

- (2) Set SPENA low to let the SPI valid.

- (3) Send "0" in the MSB to show writing the SPI and the address 4-bits (A3: MSB, A0: LSB) in the rising edge of the SPCK then read the data(D7: MSB, D0: LSB) in the rising edge of the SPCK.

#### 7.2 Follow

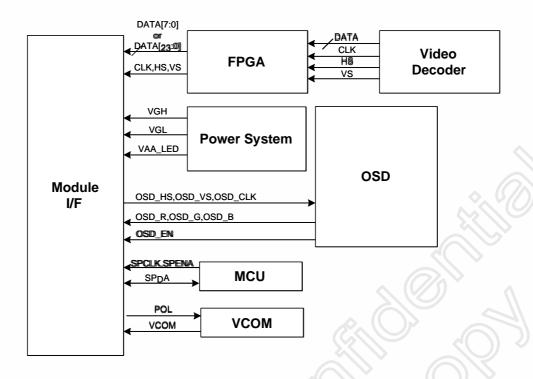

## 8. System Block Diagram

Himax Confidential

-P.8-